| Placing values onto variables and nets are called assignments. There are three necessary forms: An assignment has two parts, right-hand side (RHS) and left-hand side (LHS) with an equal symbol (=) or a less than-equal symbol (<=) in between. | Assignment Type | Left-hand Side | | Procedural | | | Continuous | | | Procedural Continuous | | The RHS can contain any expression that evaluates to a final value while the LHS indicates a variable or net to which RHS's value is being assigned. Procedural AssignmentProcedural assignments occur within procedures such as initial, always, task , and functions are used to place values onto variables. The variable will hold the value until the next assignment to the same variable. The value will be placed onto the variable when the simulation executes this statement during simulation time. This can be modified and controlled the way we want by using control flow statements such as if-else-if, looping , and case statement mechanisms. Variable Declaration Assignment An initial value can be placed onto a variable at the time of its declaration. The assignment does not have the duration and holds the value until the next assignment to the same variable happens. NOTE: The variable declaration assignments to an array are not allowed.If the variable is initialized during declaration and at 0 times in an initial block as shown below, the order of evaluation is not guaranteed, and hence can have either 8'h05 or 8'hee. Continuous AssignmentThis is used to assign values onto scalar and vector nets. And it happens whenever there is a change in the RHS. It provides a way to model combinational logic without specifying an interconnection of gates and makes it easier to drive the net with logical expressions. Whenever b or c changes its value, the whole expression in RHS will be evaluated and updated with the new value. Net Declaration Assignment This allows us to place a continuous assignment on the same statement that declares the net. NOTE: Only one declaration assignment is possible because a net can be declared only once.Procedural continuous assignment. These are procedural statements that allow expressions to be continuously assigned to variables or nets. And these are the two types. 1. Assign deassign: It will override all procedural assignments to a variable and deactivate it using the same signal with deassign . The value of the variable will remain the same until the variable gets a new value through a procedural or procedural continuous assignment. The LHS of an assign statement cannot be a part-select, bit-select, or an array reference, but it can be a variable or a combination of the variables. 2. Force release: These are similar to the assign deassign statements but can also be applied to nets and variables. The LHS can be a bit-select of a net, part-select of a net, variable, or a net but cannot be the reference to an array and bit or part select of a variable. The force statement will override all other assignments made to the variable until it is released using the release keyword.  - Send your Feedback to [email protected]

Help Others, Please Share Learn Latest Tutorials Transact-SQL  Reinforcement Learning  R Programming  React Native  Python Design Patterns  Python Pillow  Python Turtle  Preparation Verbal Ability  Interview Questions  Company Questions Trending Technologies Artificial Intelligence  Cloud Computing  Data Science  Machine Learning  B.Tech / MCA Data Structures  Operating System  Computer Network  Compiler Design  Computer Organization  Discrete Mathematics  Ethical Hacking  Computer Graphics  Software Engineering  Web Technology  Cyber Security  C Programming  Control System  Data Mining  Data Warehouse  09 Sep 2021In Verilog, there are various ways for assignment, due to the concurrent nature of the Verilog code. Also, to represent the combinational and sequential digital circuits, Verilog provides different ways for assignment which helps to model the hardware accurately. As we know, Verilog has net and reg data types, which represent a wire and flip flop respectively. From hardware point of view, wires are driven continuously once the circuit is switched on, thus for every point of time wire will take the value which is fed into as it cannot retain any previous value. To represent this behaviour, Verilog provides continuous assignment. This will assign certain value to the wire at every time step. Similarly, flip flops, are not driven continuously, rather it is driven at some clock edge or any other event, as flip flops retain the value until it is changed. This is the expected behaviour in sequential circuits. To represent this behaviour, Verilog provides procedural assignment, in which the assignment will be done only if certain event is triggered. Let’s see these assignments in detail. Continuous AssignmentAs discussed earlier this assignment is generally used for net data types. assign keyword is used for continuous assignment and is used directly inside the module, i.e., procedural blocks are not required for this type of assignment. Procedural AssignmentProcedural assignments are used with flip flops, i.e., for sequential circuits. Thus, it can be used to drive only variables and not any net data type. Also, this type of assignment can only be used inside a procedural block, i.e., initial or always . Procedural assignment can further be divided into 2 types: Blocking AssignmentThis type of assignment is the same as we see in all the programming language. As the name suggests, program flow will be blocked until the assignment is complete. This assignment is done using the help of = operator, which is also known as blocking assignment operator. Blocking assignment is executed in the Active region of the event semantics . As we know, the active region does not guarantee the order of execution, thus this type of assignment is prone to race conditions as discussed in previous article. Non-blocking AssignmentThis type of assignment, as name suggests, does not block the flow of program. The RHS of the assignment operation is calculated but it is not assigned to LHS. All the non-blocking assignments are executed at the end of the time-step in NBA region of event semantics and the LHS gets assigned with the calculated RHS. NBAs are done using <= operator which is also known as non-blocking assignment operator. As this assignment is done in NBA region, it helps prevent race around condition. We will see how this prevents race around condition with example later in this article. Procedural Continuous AssignmentThis is a continuous assignment which is used inside the procedural blocks. This is mainly used when we want to override the value of a variable or net. These types of assignments can be achieved using - assign - deassign keyword

- force - release keyword.

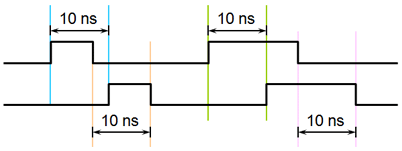

Assign deassign keywordsThese are used to override the value of a variable until the variable is de-assigned using deassign keyword. After de-assignment, the value of the variable will remain the same until it is re-assigned using procedural or procedural continuous assignment. These can be used only used when LHS is a variable or concatenation of variable. In below example, the value of a is continuously incremented in the first initial block. In the second initial block, at t=17 , the value of a is overridden using assign keyword, and thus the value of a is not getting incremented. Once deassign is used at t=27 , the value of a starts getting incremented. The value of a is not getting printed once the value of a is overridden, as $monitor prints only when the value of the variable changes. As assign does not let the value change, thus value of a is not getting printed even after a is incremented. Force release keywordThese are same as that of assign-deassign statement but it can be used for both nets and variables. The LHS can be a bit-select, part-select of net but cannot be an array or a bit or part select of variables. These will override all other assignments until released. In below example, b is continuously assigned ~a , i.e., inverse of a. In first initial block value of a is incremented and the value of b also changes. In second initial block, at t=15 value of a is overridden using force keyword. Value of b changes with response to a . At t=25 value of b[2:1] is overridden with force keyword, and thus now only the first and last bit of b can change. At t=35 variable a is released, and value of a can be changed, but net b is still not released, so only the first and the last bit of b changes with change in a . At t=45 net b is also released and now all bits of b is changed with change in a . Prevention of race around conditionRace around condition, which was discussed in earlier article , can be prevented by using a non-blocking assignment. As we know in non-blocking assignment, the LHS is assigned in the non-blocking region of event semantics, which comes after the active regions, thus the value is determinate as all the calculations have been already done. Let’s understand this with an example. In the 1st code, at the positive edge of clk , variable a is assigned a value whereas at the same time b is reading of value of a . As order of execution in active region is not guaranteed in Verilog, thus it can lead to a race around condition. Whereas in 2nd code, as non-blocking assignment is used, thus 1 will not be assigned immediately to a . Now when, b access the variable a it will always read the previous value stored, in this case 0 . Thus, b will be assigned with 0 and a will be assigned with 1 at the send of the time step. Also note that for b to attain the value of a , it takes 2 cycles, thus at t=30, b = 1 1st code - having race around condition2nd code - solution for race condition. - Introduction to Verilog

- Verilog Event Semantics

- Basics of Verilog

- Verilog Syntax

- Data Types in Verilog

- Verilog Vectors

- Verilog Arrays

- Verilog Modules

- Verilog Ports

- Verilog Operators

- Verilog Procedural Blocks

- Different types of loops in Verilog

- Conditional Statements in Verilog

- Verilog functions and tasks

- Compiler Directives in Verilog

- Verilog System Functions

- Delays in Verilog

Stack Exchange NetworkStack Exchange network consists of 183 Q&A communities including Stack Overflow , the largest, most trusted online community for developers to learn, share their knowledge, and build their careers. Q&A for work Connect and share knowledge within a single location that is structured and easy to search. Difference between blocking and nonblocking assignment VerilogI was reading this page http://www.asic-world.com/verilog/verilog_one_day3.html when I came across the following: We normally have to reset flip-flops, thus every time the clock makes the transition from 0 to 1 (posedge), we check if reset is asserted (synchronous reset), then we go on with normal logic. If we look closely we see that in the case of combinational logic we had "=" for assignment, and for the sequential block we had the "<=" operator. Well, "=" is blocking assignment and "<=" is nonblocking assignment. "=" executes code sequentially inside a begin / end, whereas nonblocking "<=" executes in parallel. I was fairly sure that nonblocking assignments were sequential while blocking assignments were parallel. After all, you can make blocking assignments with assign statements outside of always blocks, and those all run in parallel. Is this a mistake, or is the behavior different inside an always block? And, if the behavior IS different inside an always block, can nonblocking assignments be made outside an always block?  3 Answers 3was fairly sure that nonblocking assignments were sequential while blocking assignments were parallel. Blocking assignment executes "in series" because a blocking assignment blocks execution of the next statement until it completes. Therefore the results of the next statement may depend on the first one being completed. Non-blocking assignment executes in parallel because it describes assignments that all occur at the same time. The result of a statement on the 2nd line will not depend on the results of the statement on the 1st line. Instead, the 2nd line will execute as if the 1st line had not happened yet.  - \$\begingroup\$ So what about assign statements? Are they just in a whole class of their own? \$\endgroup\$ – Void Star Commented Nov 24, 2013 at 4:25

- 6 \$\begingroup\$ Yes, assign statements occur outside of always blocks and are generally used to describe to combinatorial (un-latched) logic (while always blocks, with some exceptions, describe sequential logic). AFAIK, assign statements always execute "in parallel" whenever their LHS has a value change. \$\endgroup\$ – The Photon Commented Nov 24, 2013 at 4:28

- \$\begingroup\$ Okay... I'm starting to get the impression that Verilog just isn't the most elegantly designed language. This is gonna be like learning C was. \$\endgroup\$ – Void Star Commented Nov 24, 2013 at 5:30

- 2 \$\begingroup\$ Verilog was designed to "describe" hardware that already exists. Using it as a language to design (synthesize) hardware is a hack. \$\endgroup\$ – The Photon Commented Nov 24, 2013 at 6:02

- 6 \$\begingroup\$ if Verilog "like learning C" is a problem, take a look at VHDL. Some people have fairly strong preferences for one or the other. To some, VHDL is just too verbose. To me, it's much better thought out. (signal/variable assignment semantics are much clearer than blocking/non for example). stackoverflow.com/questions/13954193/… and sigasi.com/content/vhdls-crown-jewel You may prefer it or hate it. But it's worth a look. \$\endgroup\$ – user16324 Commented Nov 24, 2013 at 10:20

Assign statements are neither "blocking" or "nonblocking", they are "continuous". The output of an assign statement is always equal to the specified function of it's inputs. "blocking" and "nonblocking" assignments only exist within always blocks. A blocking assignment takes affect immediately it is processed. A nonblocking assignment takes place at the end of processing the current "time delta". always blocks can be used to model either combinatorial or sequential logic (systemverilog has always_comb and always_ff to make this explicit). When modeling combinatorial logic it's usually more efficient to use = but it typically doesn't really matter. When modelling sequential logic (e.g. always @(posedge clk) ) you normally use nonblocking assingments. This allows you to deterime the "state after the clock edge" in terms of "the state before the clock edge". It is sometimes useful to use blocking assignments in sequential always blocks as "variables". If you do this then there are two key rules to bear in mind. - Do not access a reg that is set with blocking assignments inside a sequential always block from outside the always block it is assigned in.

- Do not mix blocking and nonblocking assignments to the same reg.

Breaking these rules is likely to result in synthesis failures and/or behaviour differences between simulation and synthesis.  - \$\begingroup\$ ""Do not access a reg that is set with blocking assignments inside a sequential always block from outside the always block it is assigned in."" Can you please explain it? \$\endgroup\$ – user125575 Commented Oct 4, 2016 at 6:44

- 2 \$\begingroup\$ Different sequential always blocks do not have a defined order. So reading a "reg" set with a blocking assingment in one always block from another always block will lead to unpredicable behaviour. \$\endgroup\$ – Peter Green Commented Oct 4, 2016 at 15:23

- \$\begingroup\$ And even if it appears to work in simulation, a synthesis tool should look at that and say "nope". I use local regs for those intermediate vars, and make sure that they are always assigned to on every clock before being read, so that no 'storage' is implied. \$\endgroup\$ – greggo Commented Mar 30, 2017 at 11:57

- \$\begingroup\$ IIRC at least in quartus it is only considered a warning not an error. \$\endgroup\$ – Peter Green Commented Mar 30, 2017 at 11:59

- \$\begingroup\$ You should not be using nonblocking assignment in combinational logic, it can lock up the simulation. For more details, refer this answer: electronics.stackexchange.com/a/506047/238188 \$\endgroup\$ – Shashank V M Commented Oct 5, 2020 at 14:55

The term Blocking assignment confuses people because the word blocking would seem to suggest time-sequential logic. But in synthesized logic it does not mean this , because everything operates in parallel . Perhaps a less confusing term would be immediate assignment , which would still differentiate the intermediate results of combinational logic from the inputs to non-transparent memory elements (for example clocked registers), which can have delayed assignment . From a legalistic standpoint, it all works out very nicely. You can, in fact, consider the = to be a blocking (time-sequential) operation even within always_comb sequences. However, the distinction between time-sequential and parallel makes absolutely no difference in this case because the always_comb block is defined to repeat until the instruction sequence converges on a stable state -- which is exactly what the hardware circuitry will do (if it meets the timing requirements). The synthesizable subset of Verilog (and especially SystemVerilog) is extremely simple and easy to use -- once you know the necessary idioms. You just have to get past the clever use of terminology associated with the so-called behavioral elements in the language.  - \$\begingroup\$ In behavioral coding styles ( as compared to RTL ), the distinction between blocking and non-blocking can be relevant. In some cases, the synthesis tool may be able to infer functionally equivalent RTL from behavioral component designs. \$\endgroup\$ – Brent Bradburn Commented Jul 21, 2015 at 17:28

- \$\begingroup\$ Of course the procedural mode of SystemVerilog, applicable especially to initial statements within program blocks, uses (time-sequential) blocking assignment exclusively. This is useful for testbench design, but generally not for RTL specification. \$\endgroup\$ – Brent Bradburn Commented Dec 18, 2015 at 18:58

Your AnswerSign up or log in, post as a guest. Required, but never shown By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .  Not the answer you're looking for? Browse other questions tagged verilog or ask your own question .- Featured on Meta

- Upcoming sign-up experiments related to tags

Hot Network Questions- (THEORY) Do Tree models output probabilities?

- Is it correct to call a room with a bath a "toilet"?

- Transforming sentences with perfect infintive

- How is Leetcode able to compile a C++ program without me writing a 'main()' function?

- Project Euler 127 - abc-hits

- How much time is needed to judge an Earth-like planet to be safe?

- Is there a way to snap Bézier curve handles to axes or angles?

- Generalized Sylow's theorem

- Does every proof need an axiom saying it works?

- Is this all part of a name or is part of it a title/moniker?

- How do languages where multiple files make up a module handle combining them into one translation/compilation unit?

- Can we study scientifically the set of facts and behaviors if we have no scientific explanation for the source, origin or underlying mechanism of it?

- Has Marvel shown Thor's hammer, Mjolnir, breaking through Invisible Woman's force fields?

- What happens if you don't appear for jury duty for legitimate reasons in the state of California?

- How to avoid init methods when 2 objects need the reference of each other?

- Is APU bleed air blow back a genuine risk on the 737-800?

- Was Croatia the first country to recognize the sovereignity of the USA? Was Croatia expecting military help from USA that didn't come?

- What was the first modern chess piece?

- tnih neddih eht kcehc

- Tool Storage Corrosion Risk

- Wiring basics for timer relay

- Why is "Colourless green ideas sleep furiously" considered meaningless?

- Who is the "Sir Oracle" being referenced in "Dracula"?

- Is the work I do on the object always equal in magnitude but opposite in sign to the work the object does on me?

Verilog: Continuous & Procedural Assignments Continuous AssignmentContinuous assignment is used to drive a value on to a net in dataflow modeling. The net can be a vector or scalar, indexed part select, constant bit or part select of a vector. Concatenation is also supported with scalar vector types. module Conti_Assignment (addr1,addr2,wr,din,valid1,valid2,dout); input [31:0] addr1,addr2; input [31:0] din; output [31:0] dout; input valid1,valid2,wr; wire valid; wire [31:0] addr; //Net (scalar) continuous assignment assign valid = valid1 | valid2; //Vector continuous assignment assign addr[31:0] = addr1[31:0] ^ addr2[31:0]; //Part select & Concatenation in Continuous assignment assign dout[31:0] = (valid & wr) ? {din[31:2],2'b11} : 32'd0; Regular & Implicit AssignmentRegular continuous assignment means, the declaration of a net and its continuous assignments are done in two different statements. But in implicit assignment, continuous assignment can be done on a net when it is declared itself. In the below example, `valid` is declared as wire during the assignment. If signal name is used to the left of the continuous assignment, an implicit net declaration will be inferred. In the below code `dout` is not declared as net, but it is inferred during assignment. module Implicit_Conti_Assignment (addr1,addr2,wr,din,valid1,valid2,dout); input [31:0] addr1,addr2; input [31:0] din; output [31:0] dout; input valid1,valid2,wr; //Net (scalar) Implict continuous assignment wire valid = (valid1 | valid2); //Implicit net declaration -dout assign dout[31:0] = (valid & wr) ? {din[31:2],2'b11} : 32'd0; Procedural AssignmentWe have already seen that continuous assignment updates net, but procedural assignment update values of reg, real, integer or time variable. The constant part select, indexed part select and bit select are possible for vector reg. There are two types of procedural assignments called blocking and non-blocking. Blocking assignment, as the name says, gets executed in the order statements are specified. The "=" is the symbol used for blocking assignment representation. Non-blocking assignment allows scheduling of assignments. It will not block the execution. The symbol "<=" is used for non-blocking assignment representation and mainly used for concurrent data transfers. Following example shows the differences in the simulation result by using blocking and non-blocking assignments. /* module Nonblocking_Assignment (addr1,addr2,wr,din,valid1,valid2,data,aout); input [31:0] addr1,addr2; input [31:0] din; output [31:0] data,aout; input valid1,valid2,wr; reg [31:0] data,aout, addr; reg valid; always @(addr1,addr2,wr,din,valid1,valid2) begin valid <= (valid1 | valid2); addr <= (addr1[31:0] | addr2[31:0]); data <= (valid & wr) ? {din[31:2],2'b11} : 32'd0; aout <= wr ? addr: {addr1[15:0],addr2[31:16]}; end initial $monitor($time,"NON-BLOCKING: Values valid1=%b, valid2=%b, wr=%b, addr1=%d, addr2=%d, data=%d, aout=%d", valid1,valid2,wr,addr1,addr2,data,aout); endmodule */ module Blocking_Assignment (addr1,addr2,wr,din,valid1,valid2,data,aout); input [31:0] addr1,addr2; input [31:0] din; output [31:0] data,aout; input valid1,valid2,wr; always @(addr1,addr2,wr,din,valid1,valid2) begin valid = (valid1 | valid2); addr = (addr1[31:0] | addr2[31:0]); data = (valid & wr) ? {din[31:2],2'b11} : 32'd0; aout = wr ? addr : {addr1[15:0],addr2[31:16]}; $monitor($time,"BLOCKING: Values valid1=%b, valid2=%b, wr=%b, addr1=%d, addr2=%d, data=%d, aout=%d", valid1,valid2,wr,addr1,addr2,data,aout); end endmodule module test; reg valid1,valid2,wr; reg [31:0] addr1,addr2,din; wire [31:0] data,aout; Blocking_Assignment Block_Assign(addr1,addr2,wr,din,valid1,valid2,data,aout); //Nonblocking_Assignment Nonblock_Assign(addr1,addr2,wr,din,valid1,valid2,data,aout); initial begin valid1 = 0; valid2 = 0; addr1 = 32'd12; addr2 = 32'd36; din = 32'd198; wr = 1; #5 valid1 = 1; #10 valid1 = 0; valid2 = 1; #10 addr1 = 32'd0; addr2 = 32'd0; #5 wr = 0; #12 wr = 1; /* ncsim> run 0NON-BLOCKING: Values valid1=0, valid2=0, wr=1, addr1= 12, addr2= 36, data= X, aout= x 5NON-BLOCKING: Values valid1=1, valid2=0, wr=1, addr1= 12, addr2= 36, data= 0, aout= 44 15NON-BLOCKING: Values valid1=0, valid2=1, wr=1, addr1= 12, addr2= 36, data= 199, aout= 44 25NON-BLOCKING: Values valid1=0, valid2=1, wr=1, addr1= 0, addr2= 0, data= 199, aout= 44 30NON-BLOCKING: Values valid1=0, valid2=1, wr=0, addr1= 0, addr2= 0, data= 0, aout= 0 42NON-BLOCKING: Values valid1=0, valid2=1, wr=1, addr1= 0, addr2= 0, data= 199, aout= 0 ncsim: *W,RNQUIE: Simulation is complete. */ /* ncsim> run 0BLOCKING: Values valid1=0, valid2=0, wr=1, addr1= 12, addr2= 36, data= 0, aout= 44 5BLOCKING: Values valid1=1, valid2=0, wr=1, addr1= 12, addr2= 36, data= 199, aout= 44 15BLOCKING: Values valid1=0, valid2=1, wr=1, addr1= 12, addr2= 36, data= 199, aout= 44 25BLOCKING: Values valid1=0, valid2=1, wr=1, addr1= 0, addr2= 0, data= 199, aout= 0 30BLOCKING: Values valid1=0, valid2=1, wr=0, addr1= 0, addr2= 0, data= 0, aout= 0 42BLOCKING: Values valid1=0, valid2=1, wr=1, addr1= 0, addr2= 0, data= 199, aout= 0 ncsim: *W,RNQUIE: Simulation is complete. ncsim> exit */ Procedural AssignmentsBlocking assignments, race around condition: a problem with blocking assignment.  Blocking and Non-blocking Assignment in Verilog- Assignment is only done in procedural block(always ot initial block)

- Both combintational and sequential circuit can be described.

- Assignment can only possible to reg type irrespect of circuit type

Let's say we want to describe a 4-bit shift register in Verilog. For this, we are required to declare a 3-bit reg type variable. The output of shift[0] is the input of shift[1], output of shift[1] is input of shift[2], and all have the same clock. Let's complete the description using both assignment operator. Non-Blocking AssignmentWhen we do synthesis, it consider non-blocking assignment separately for generating a netlist. If we see register assignment in below Verilog code, all register are different if we consider non-blocking assignment separately. If you do the synthesis, it will generate 3 registers with three input/output interconnects with a positive edge clock interconnect for all register. Based on the Verilog description, all are connected sequentially because shift[0] is assigned d, shift[1] is assigned shift[0], and shift[2] is assigned shift[1]. Blocking AssignmentIf we use blocking assignment and do the syhtheis, the synthesis tool first generate netlist for first blocking assignment and then go for the next blocking assignment. If in next blocking assignment, if previous output of the register is assigned to next, it will generate only a wire of previously assigned register. In below Verilog code, even though all looks three different assignment but synthesis tool generate netlist for first blocking assigment which is one register, working on positive edge of clock, input d and output shift[0]. Since blocking assignment is used, for next blocking assignment, only wire is generated which is connected to shift[0]. Same is for next statement a wire is generated which is connected to shift[0]. Click like if you found this useful Add Comment This policy contains information about your privacy. By posting, you are declaring that you understand this policy: - Your name, rating, website address, town, country, state and comment will be publicly displayed if entered.

- Your IP address (not displayed)

- The time/date of your submission (displayed)

- Administrative purposes, should a need to contact you arise.

- To inform you of new comments, should you subscribe to receive notifications.

- A cookie may be set on your computer. This is used to remember your inputs. It will expire by itself.

This policy is subject to change at any time and without notice. These terms and conditions contain rules about posting comments. By submitting a comment, you are declaring that you agree with these rules: - Although the administrator will attempt to moderate comments, it is impossible for every comment to have been moderated at any given time.

- You acknowledge that all comments express the views and opinions of the original author and not those of the administrator.

- You agree not to post any material which is knowingly false, obscene, hateful, threatening, harassing or invasive of a person's privacy.

- The administrator has the right to edit, move or remove any comment for any reason and without notice.

Failure to comply with these rules may result in being banned from submitting further comments. These terms and conditions are subject to change at any time and without notice. Comments (1) hey in blocking assignment do we get shift in data i dont think so . we get all values same and equal to d. Please do not focus on the module name; focus on how the netlist is generated after the synthesis.  Verilog Blocking & Non-BlockingBlocking assignment statements are assigned using = and are executed one after the other in a procedural block. However, this will not prevent execution of statments that run in a parallel block. Note that there are two initial blocks which are executed in parallel when simulation starts. Statements are executed sequentially in each block and both blocks finish at time 0ns. To be more specific, variable a gets assigned first, followed by the display statement which is then followed by all other statements. This is visible in the output where variable b and c are 8'hxx in the first display statement. This is because variable b and c assignments have not been executed yet when the first $display is called. In the next example, we'll add a few delays into the same set of statements to see how it behaves. Non-blockingNon-blocking assignment allows assignments to be scheduled without blocking the execution of following statements and is specified by a symbol. It's interesting to note that the same symbol is used as a relational operator in expressions, and as an assignment operator in the context of a non-blocking assignment. If we take the first example from above, replace all = symobls with a non-blocking assignment operator , we'll see some difference in the output. See that all the $display statements printed 'h'x . The reason for this behavior lies in the way non-blocking assignments are executed. The RHS of every non-blocking statement of a particular time-step is captured, and moves onto the next statement. The captured RHS value is assigned to the LHS variable only at the end of the time-step. So, if we break down the execution flow of the above example we'll get something like what's shown below. Next, let's use the second example and replace all blocking statements into non-blocking. Once again we can see that the output is different than what we got before. If we break down the execution flow we'll get something like what's shown below.  - The Verilog-AMS Language

- Initial and Always Processes

- Assignment Statements

Assignment Statements Blocking assignment . A blocking assignment evaluates the expression on its right hand side and then immediately assigns the value to the variable on its left hand side: It is also possible to add delay to a blocking assignment. For example: In this case, the expression on the right hand side is evaluated and the value is held for 10 units of time. During this time, the execution of the code is blocked in the middle of the assignment statement. After the 10 units of time, the value is stored in the variable on the left Nonblocking Assignment A nonblocking assignment evaluates the expression on its right hand side without immediately assigning the value to the variable on the left. Instead the value is cached and execution is allowed to continue onto the next statement without performing the assignment. The assignment is deferred until the next blocking statement is encountered. In the example below, on the positive edge of clk the right-hand side of the first nonblocking assignment is evaluated and the value cached without changing a. Then the right-hand side of the second nonblocking assignment statement is evaluated is also cached without changing b. Execution continues until it returns to the event statement, once there the execution of the process blocks until the next positive edge of the clk. Just before the process blocks, the cached values finally assigned to the target variables. In this way, the following code swaps the values in a and b on every positive edge of clk: Adding delay to nonblocking assignments is done as follows: Using nonblocking assignment with delay in this manner is a way of implementing transport delay , as shown below:  Blocking versus Nonblocking Assignment Nonblocking statements allow you to schedule assignments without blocking the procedural flow. You can use the nonblocking procedural statement whenever you want to make several register assignments within the same time step without regard to order or dependence upon each other. It means that nonblocking statements resemble actual hardware more than blocking assignments. Generally you would use nonblocking assignment whenever assigning to variables that are shared between multiple initial or always processes if the statements that access the variable could execute at the same time. Doing so resolves race conditions. Blocking assignment is used to assign to temporary variables when breaking up large calculations into multiple assignment statements. For example: Procedural Continuous Assignment Two types of continuous assignment are available in initial and always processes: assign and force . The target of an assign statement must be a register or a concatenation of registers. The value is continuously driven onto its target and that value takes priority over values assigned in procedural assignments. Once a value is assigned with an assign statement, it can only be changed with another assign statement or with a force statement. Execution of deassign releases the continuous assignment, meaning that the value of the register can once again be changed with procedural assignments. For example, the following implements a D-type flip-flop with set and reset: Assign statements are used to implement set and reset because they dominate over the non-blocking assignment used to update q upon positive edges of the clock c . If instead a simple procedural assignment were used instead, then a positive edge on the clock could change q even if r or s were high. A force statement is similar to assign , except that it can be applied to both registers and nets. It overrides all other assignments until the release statement is executed. Force is often used in testbenches to eliminate initial x-values in the DUT or to place it in a particular state. For example: - Stack Overflow Public questions & answers

- Stack Overflow for Teams Where developers & technologists share private knowledge with coworkers

- Talent Build your employer brand

- Advertising Reach developers & technologists worldwide

- Labs The future of collective knowledge sharing

- About the company

Collectives™ on Stack OverflowFind centralized, trusted content and collaborate around the technologies you use most. Q&A for work Connect and share knowledge within a single location that is structured and easy to search. Get early access and see previews of new features. Easy way to assign values to an array in Verilog?So I'm creating a large FIR filter in Verilog, it has 256 taps. So I need 256 coefficients. I want to try and make my code as modular as possible so I wonder if there's a way to create another external file to the FIR module which contains the values for the coefficients? Currently the only I know to assign values to an array in Verilog is like the following: But when you have 256 values to assign this is a very long process manually organising the code, even with Find/Replace you can only do so much. What I want is the ability to assign values to arrays like you can in System Verilog: I don't want to use System Verilog as it isn't as widely used. How can I do this?  - Do you need this only for simulation or do you need the array of constants to be synthesizable? – dwikle Commented May 2, 2015 at 11:24

- I want then to be synthesizable. – George Waller Commented May 2, 2015 at 12:35

- This question is no longer relevant as SystemVerilog is now widely used, and has features exactly to address this requirement – dave_59 Commented Sep 26, 2022 at 17:06

If the values (coefficients) is saved in an external file (for example 'file.txt'), you can use system functions in simulation ( $fscanf ) to read the values from the file and wirte them on the datafile ( datafile is an array). In the following code I assumed that you have 256 values is saved in the external file ('file.txt') and I tried to read the values 256 times from 'file.txt' and write them on the datafile : System functions are not synthesizable. It's for simulation. If you want to write a synthesizable code, I suggest the following way :  - Thank you. I assume this executes at compile time? – George Waller Commented May 2, 2015 at 12:35

- @George waller, I completed my answer with a synthesizable code. – Amir Commented May 2, 2015 at 15:40

Your AnswerReminder: Answers generated by artificial intelligence tools are not allowed on Stack Overflow. Learn more Sign up or log inPost as a guest. Required, but never shown By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy . Not the answer you're looking for? Browse other questions tagged arrays verilog or ask your own question .- Featured on Meta

- Upcoming sign-up experiments related to tags

- The 2024 Developer Survey Is Live

- The return of Staging Ground to Stack Overflow

- Policy: Generative AI (e.g., ChatGPT) is banned

Hot Network Questions- Is the work I do on the object always equal in magnitude but opposite in sign to the work the object does on me?

- Where do I clear immigration London to Mumbai to Chennai?

- How can I permute pair of elements in a list?

- Am I wasting my time self-studying program pre-requisites?

- Why is the Newcomb problem confusing?

- Wiring basics for timer relay

- Find 10 float64s that give the least accurate sum

- Was Croatia the first country to recognize the sovereignity of the USA? Was Croatia expecting military help from USA that didn't come?

- Does anyone know what Psatlees is more than it has something to do with silk?

- Understanding the implication in linear algebra regarding vectors

- A Fantasy movie with a powerful humanoid being that lives in water

- Is it correct to call a room with a bath a "toilet"?

- select() / poll() timeout stretches on Linux

- Cannot install gnome-control-center upon upgrading Ubuntu (unmet dependencies with libpython3.10)

- watering for a snatch - what does it mean?

- Creating a property list. I'm new to expl3

- Should I practise a piece at a metronome tempo that is faster than required?

- What aspects define how present the garlic taste in an aglio e olio pasta becomes?

- How should I report a Man-in-the-Middle attack in my workplace?

- Is this crumbling concrete step salvageable?

- What is the meaning of this black/white (likely non-traffic) sign seen on German highways?

- Why is "Colourless green ideas sleep furiously" considered meaningless?

- Finding a mystery number from a sum and product, with a twist

- Balls of different weights: how few balls can there be?

|

COMMENTS

Procedural assignments occur within procedures such as always, initial, task and functions and are used to place values onto variables. The variable will hold the value until the next assignment to the same variable. The value will be placed onto the variable when the simulation executes this statement at some point during simulation time.

Procedural assignments are used for updating register data types and memory data types. The expression in a blocking procedural assignment is evaluated and assigned when the statement is encountered.

Verilog assign statement. Signals of type wire or a similar wire like data type requires the continuous assignment of a value. For example, consider an electrical wire used to connect pieces on a breadboard. As long as the +5V battery is applied to one end of the wire, the component connected to the other end of the wire will get the required ...

And these are the two types. 1. Assign deassign: It will override all procedural assignments to a variable and deactivate it using the same signal with deassign. The value of the variable will remain the same until the variable gets a new value through a procedural or procedural continuous assignment.

For example, in this code, when you're using a non-blocking assignment, its action won't be registered until the next clock cycle. This means that the order of the assignments is irrelevant and will produce the same result. The other assignment operator, '=', is referred to as a blocking assignment. When '=' assignment is used, for the purposes ...

1. Evaluate a | b, assign result to x. 2. Evaluate a^b^c, assign result to y. 3. Evaluate b&(~c), assign result to z. end. Nonblocking assignment: all assignments deferred until all right-hand sides have been evaluated (end of simulation timestep) always @ (a or b or c) begin.

Verilog Assignments. 09 Sep 2021. 6 mins. In Verilog, there are various ways for assignment, due to the concurrent nature of the Verilog code. Also, to represent the combinational and sequential digital circuits, Verilog provides different ways for assignment which helps to model the hardware accurately. As we know, Verilog has net and reg data ...

Evaluate b&(~c) but defer assignment of z 1. Evaluate a | b, assign result tox x 2. Evaluate a^b^c, assign result to y 3. Evaluate b&(~c), assign result to zz I. Blocking vs. Nonblocking Assignments • Verilog supports two types of assignments within always blocks, with subtly different behaviors. • Blocking assignment: evaluation and ...

• Non-blocking assignments literally do not blockthe execution of the next statements. The right side of all statements are determined first, then the left sides are assigned together. - Consequently, non-blocking assignments result in simultaneous or parallel statement execution. For example: assume a = b = 0 initially; a <= 1; b <= a;

The answer to this question is strongly related to Verilog concepts I described in my answer to another question about Verilog non-blocking assignment (NBA).. The straightway answer to your question is very simple: all assignments are performed at the same simulation time slot, i.e. both blocking and non-blocking assignments will be evaluated and assigned before the following time slot (which ...

In conclusion, completing your Verilog assignment can be a rewarding experience with the right approach. By understanding the requirements, planning your design, writing modular code, testing ...

Blocking assignment executes "in series" because a blocking assignment blocks execution of the next statement until it completes. Therefore the results of the next statement may depend on the first one being completed. Non-blocking assignment executes in parallel because it describes assignments that all occur at the same time.

Continuous assignment is used to drive a value on to a net in dataflow modeling. The net can be a vector or scalar, indexed part select, constant bit or part select of a vector. Concatenation is also supported with scalar vector types. module Conti_Assignment (addr1,addr2,wr,din,valid1,valid2,dout); input [31:0] addr1,addr2; input [31:0] din ...

The procedural assignments can also be placed directly inside a module while declaring a variable. (Ex. reg [3:0] i_data = 4'h7) There are two types of procedural assignments and both of them are widely used in the designs written in the Verilog language. Blocking assignments; Non-blocking assignments

Blocking and Non-blocking Assignment in Verilog. When working with behavioural modeling in Verilog, there are two types of assigment which is known as blocking and non blocking assigment and both of them there is a operator, '=' operator for blocking assignment and '=' operator for non blocking assigment.At short, blocking assignment executes one by one sequentially and non-blocking assignemnt ...

The RHS of every non-blocking statement of a particular time-step is captured, and moves onto the next statement. The captured RHS value is assigned to the LHS variable only at the end of the time-step. Simulation Log. ncsim> run. [0] a= 0xx b= 0xx c= 0xx. [0] a= 0xx b= 0xx c= 0xx. [0] a= 0xx b= 0xx c= 0xx.

Blocking Assignment. A blocking assignment evaluates the expression on its right hand side and then immediately assigns the value to the variable on its left hand side: a = b + c; It is also possible to add delay to a blocking assignment. For example: a = #10 b + c; In this case, the expression on the right hand side is evaluated and the value ...

Few examples on Verilog assignment. If you refer to v2005 LRM, there are 2 interesting definitions, an extract of which is pasted below - 6.1 Continuous assignments

datafile[6] = 55938; datafile[7] = 58764; end. But when you have 256 values to assign this is a very long process manually organising the code, even with Find/Replace you can only do so much. What I want is the ability to assign values to arrays like you can in System Verilog: reg [15:0] datafile [8] = '{8468,56472,56874,358,2564,8498,4513,9821};